알쏭달쏭 공부한거 쓰기

20241203 13장 clock _generators & 555 timer Ic 본문

Square Wave를 만드는 회로들에 대한 내용입니다.

555 Timer IC를 이용하는 방법도 다룹니다.

트렌지스터를 스위치로 쓰는 회로는 헷갈릴 것 같아서

pulse 파를 만들어내는 회로에 대해서 배울 예정.

슈미트 트리거와 적분기 회로를 맞물려놓으면 삼각파와 펄스파를 만드어 내는 회로가 클럭 제너레이트 회로에 들어가는 블럭임.

우리가 만드는 회로는 555IC를 이용해서 원하는 듀티사이클과 펄스파를 만들어내도록 할것임.

왜 필요할까

특정 주파수의 펄스파형이 필요한 경우가 있음.

내부안에서 자체적으로 (local)클럭을 발생시키는 회로가 내장되어 있어야함.

pcb회로는 외부에서 끌어올 수 있는 회로가 있는데 IC회로는 내부적으로 신호를 발생하는 회로블록이 들어가있어아함.

IC설계하는 엔지니어가 많이 사용하는Ring oscillator에 대해 설명

555타이머 IC를 이용해서 펄스를 만들 수 있음.

Ring oscillator

IC내부회로에 필수임.

어떻게 구성되어 있는가. not gate로 연결되어 있음.

pmos, nmos를 붙이면 not 게이트 역할함. 이 not 게이트를 홀수게 연결해서 ring의 형태로 피드백으로 연결함.

-not 게이트(인버터)의 특성에 대해 배우고 나서 링 오실레이터를 배우는데 너무 길어져서 생략.

가정: 만약 이 not gate회로에서 입력과 출력에 해당하는 노드에서 0,1도 아닌 상태에서 일정하게 유지가 될 수 있으려면

모든 입출력이 동일해야함.

ex) 모두 2.5v이면 전체 전압 2.5로 고정됨.

이론적으로는 가능 , 실제적으로 불가능함.

>노이즈가 전압에 같이 들어가면 1,0으로 나옴.

여기에 사용되는 인버터들이 논리1,0으로 결정된다고 가정함.

첫번째 not gate의 입력이 1> 출력0> 두번째 출력1>세번째 출력 0

마지막 출력 0이 loop를 통해 첫번쨰 인버터로 0이 들어감 > 1>0>1

1>0>1>0

0>1>0>1

...

Q가 1,0으로 반복된다.

clock이라고 부르는 square pulse 파를 만들어냄.

IC 회로 안에 커패시터를 넣기 쉽지 않음.

c가 작으면 넣을 수 있는데 c가 크면 IC내부 면적을 모두 차지해서 넣을 수 없음. (외부에서 커패시터로 연결함. )

커패시터를 안쓰고도 클럭을 만들어내는 기본적인 회로가 링 오실레이터 블럭임.

원하는 주파수로 나오도록 만들어아햠. 위의 수식으로 결정이도니다.

tp : not gate의 한개에 입력이 들어가서 출력이 나오는데 걸리는 시간.-전파지연시간-propagation delay time

N : not gate 의 갯수

전파지연시간이 걸리는 이유 :인버터를 이루고있는 회로를 들여다 보면 여러개의 트렌지스터나 다이오드가 들어가있음.

pn접합으로 이루어져 있어 모두 내부 기생커패시터가 존재함. 이 커패시터를 충전하고 나서야 동작을 할 수 있으므로 딜레이가 발생함.

이 값이 굉장히 작음 nsec단위이지만 지연시간을 이용해서 클락을 만들어내는 것

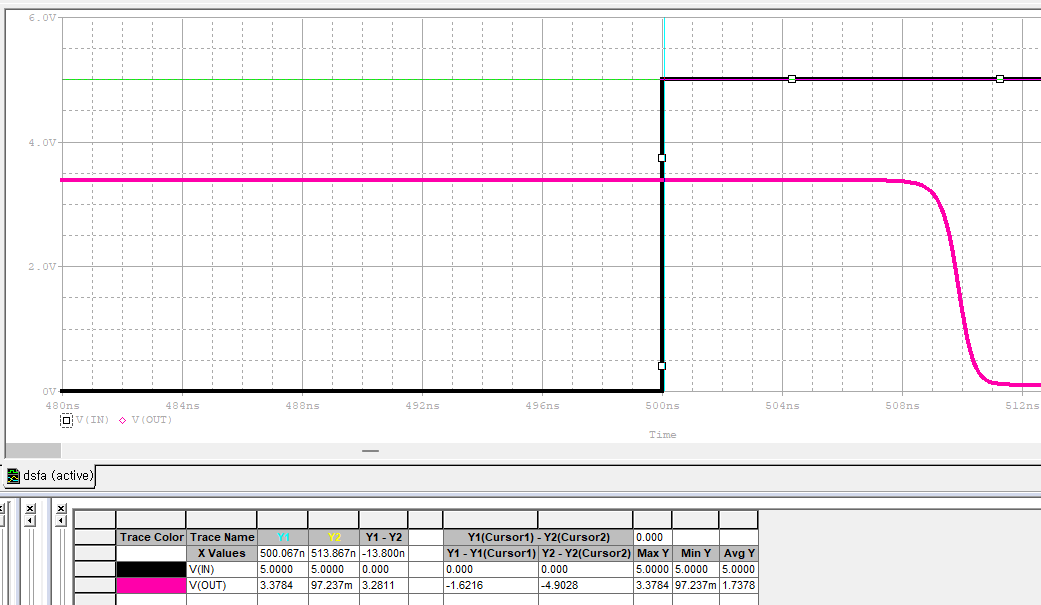

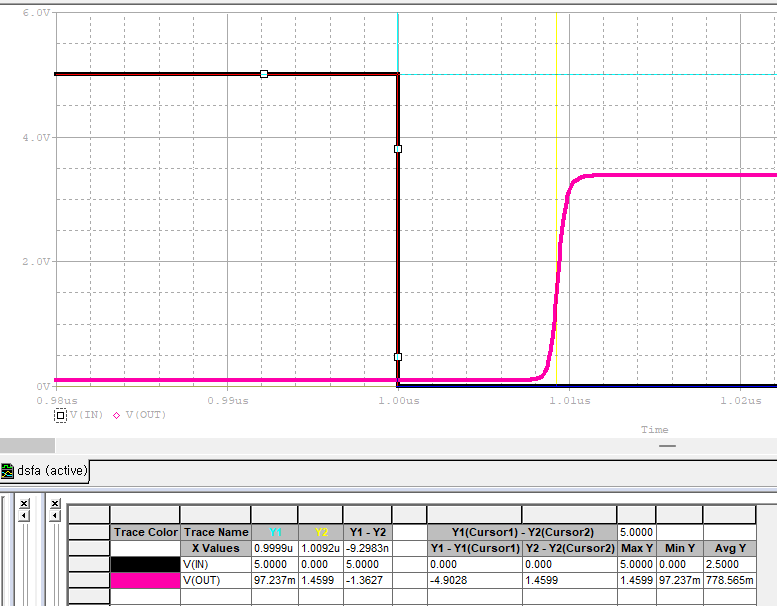

전파지연시간 tp의 정의 (잘 봐야함)

tp=tphl+tplh/2

입력이 low>high로 변하면 not의 출력이 high>low로 변하는데 출력에서 지연이 발생함.

출력이 기준> 출려이 high에서 low로 떨어지는데 걸리는 시간.: tPHL

측정방법: 입력의 한가운데 지점과 출력의 한 가운데 지점의 차이가 전파지연시간이 된다.

출력이 low에서 high로 변하는데 걸리는 시간 : tPLH라고 한다.

최종 전파지연시간 tp= 두값의 평균값을 의미함.

not gate 1개의 전파지연시간 tp

not gate가 3개 전파지연시간이 3번.

한 주기라는 것은 논리1,0이 다나와야하마.

1>0>1이 되는 것이 한 주기. (2 사이클을 돌아야함)

Fosc=1/2*N*tp가 되어야함.

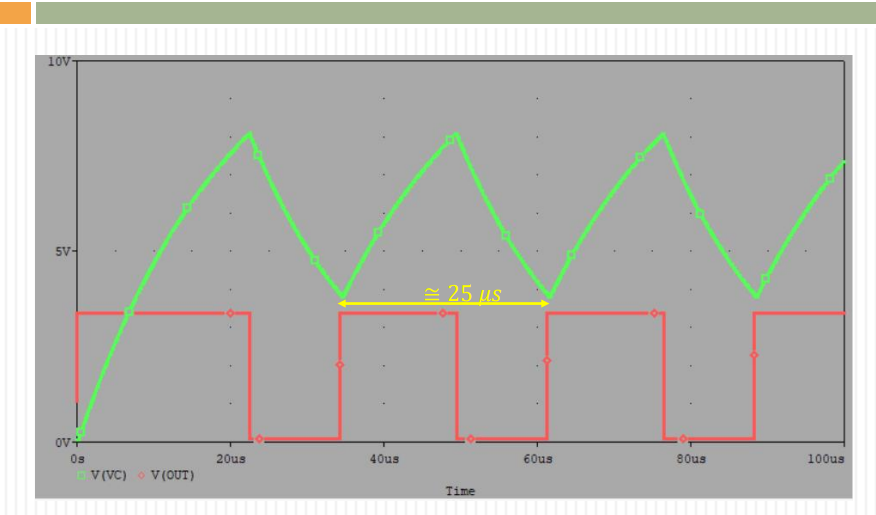

[시뮬레이션 ]

74 시리즈>74LS(low power series)>74LS04의 not

Vpulse

-pulse setting ideal pulse를 만들기 위해 TR,RF는 1ps로 입력.

주기1us 주파수1MHz clock으로 변함

듀티사이클 50 올라가고 내려가는 건 거의 수직 변화가 낫게이트의 입력으로 들어감.

출력: notgate 0V가 나올것으로 예측.

-실제로는 0v보다 살짝 높게 나옴.

논리게이트같은 경우에는 논리1,0에 해당하는 입력 범위와 출력범위가 있음(범위로 동작함. ) .

5v로 동작하는 74시리즈는 3-5v로 나오면 논리1에 해당하는 값임.

2주기를 위해 2us

촘촘히 0.1us

출력을 연결하지 않아도 전압측정 마커가 검게 된어 측정이 된다.

timing도가 나옴.

출력의 변화, 딜레이를 보고 싶음. > 타이밍도를 바꿔야함. >출력에 저항을 달아주면 된다.

저항을 달아주면 평소의 그래프가 나옴.

입출력의 시간딜레이가 나오는 것을 볼 수 있음.

확대해서 정확히 보기

논리1 3.378

논리0 97.237m

로 나옴.

전파지연시간이 9.8ns와 9.3정도 나옴. 그 평균값이 전파지연시간.

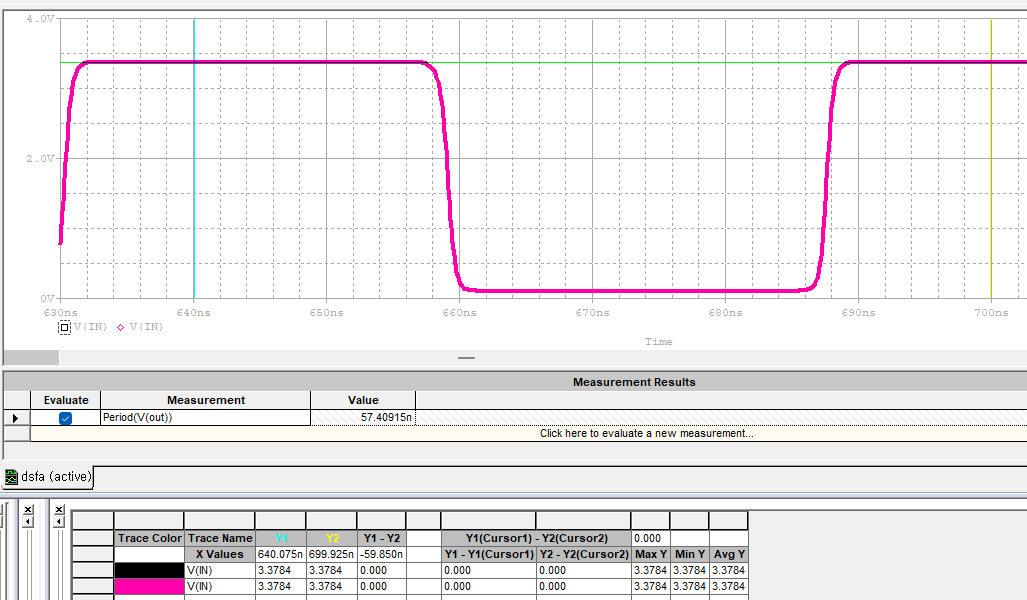

링

skip해야 클럭파형이 나옴

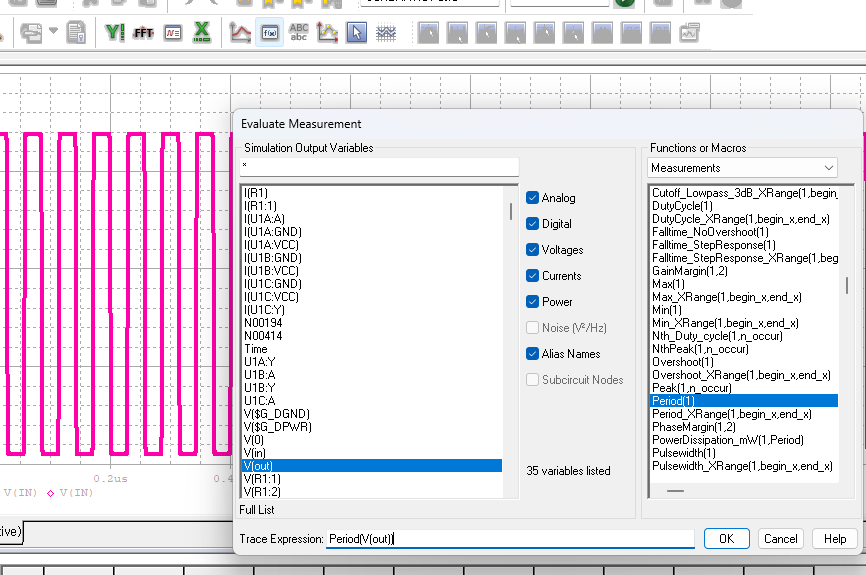

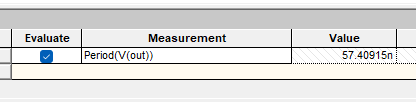

주기 측정해서 주파수 파악하는 방법

-비슷하게 보이는 값을 두개를 측정해서 주기 측정하기

-measure기능을 이용해서 데이터 찾기

주기 59.850

Vout의 주기를 파악해라는 명령어 (자동 측정)

용어 정리

-Astable

stable :안정한

논리1,0이 나오는 디지털 시스템에서 stable의 의미는 논리1, 0의 상태를 계속 유지할 수 있다는 의미 .

monostable 단안정 : 출력이 논리 0이 나오다 논리1 이 한번 나왔다 다시 0으로 유지하는 것을 단안정이라고함

bistable 쌍안정: 논리1, 논리0의 2가지 상태를 안정적으로 유지하는 회로 >대표적인 회로: 슈미트 트리거

Astable 비안정(불안정은 unstable 안정하고 싶음) 안정한게 목적이 아님 논리1,0이 번갈아가며 나옴> 펄스파, sqaure wave>반전슈미트회로에서 피드백에 RC 연결하면 비안정회로가 된다.

인버팅 슈미트 트리거 이용 RC를 이용해서 피드백을 연결하면 astable회로를 만들 수 있다.

-아이패드에 슈미트트리거와 RC피드백회로의 충방전으로 클럭 주파수에대한 정성적 해석을 함.

-아래는 정량적으로 수식으로 해석하는 방법

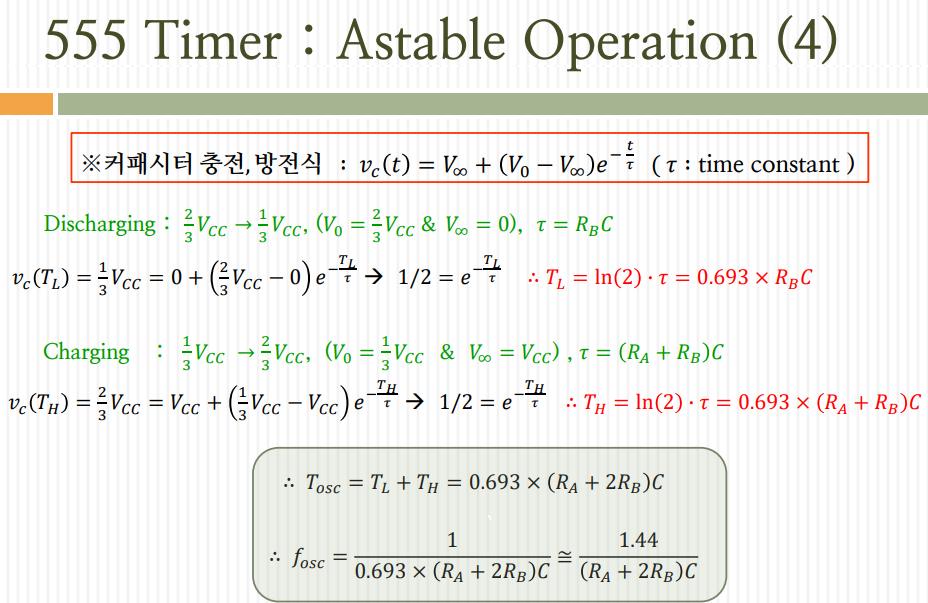

충전+방전되는 과정이 한 주기임.

충방 과정이 누구에 의해서 시간이 결정되는 건 RC 시정수에 의해 결정된다.

V무한대(무한대의 시간이 흐른 후 최종적으로 갖는 전압값)

V0(충방시작시점의 전압)

커패시터 전압이 VUT-VLT사이에서 변할 것임.

충전을 안한 상태라면 VLT에서 시작>> Vosat까지 충전이 된다.

발진주파수 찾기가 문제임.

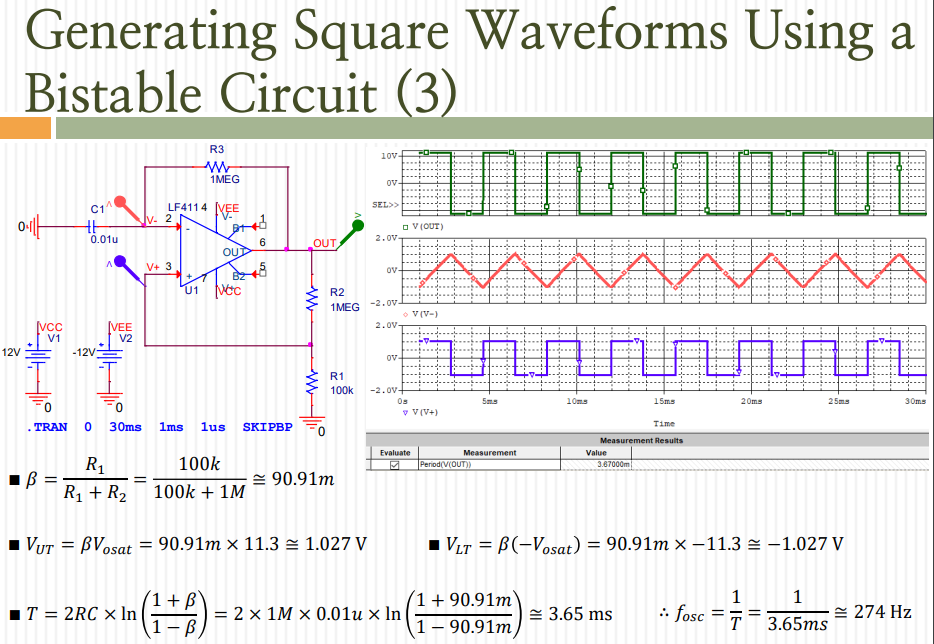

LF411

supply 전압 +-12v로 걸었음.

Vosat, -Vosat만 제공시 Vosat,-vosat의 값을 찾아야함.

opamp무엇을 쓰고 공급전압을 제공해줬으면 알아서 찾아야함.

문제를 낼때는 Vosat,-vosat을 주지만 회로설계할때는 직접 찾아야함.

12v보다 작은+-11.4v정도가 Vosat,-Vosat으로 나옴.

0v, Vcc전압을 걸어주면 작동함.

Vcc:5V-15V

원하는 듀티사이클로 나오도록.

출력이 전압으로 나옴.

출력전압으로 다른 블럭에 연결할때 생각해야할 것.

-전압이 잘 전달되기 위한 조건(크기가 변화없이 잘 넘어가는가)

-전압이 나오는 곳에서 전류공급을 할 수 있는지(뒷단이 잘 작동하도록)

뒷단에 PWD신호, 혹은 direct로 뒷단 부하를 구동시킬 수 있음.

out로 나오는 뒷단에 모터가 달려있어 돌려면 파워를 받아야함> 전압, 전류 둘다 받아야함.

ex_ 300mA정도 필요하다면 555타이머로 모터를 구동시킬 수 없음 .out단자에 전류를 보낼 수 있는 양이 200mA임.

>이런경우

555timer은 on/off 스위치회로로 들어가고 별도의 전원이 모터에 연결되도록 꾸며야함.

TTL회로의 입력으로 쓸 수 있다.(트랜지스터 트랜지스터 로직 74시리즈 (BJT)의 논리게이트의 내부가 트렌지스터끼리 연결되어 있어 TTL (BJT로구성된)회로를 의미한다.<>CMOS회로

3-5v의 전압 범위가 들어오면 1로 받는다.

0-0.5v의 전압 범위가 들어오면 0으로 받는다.

디지털 회로 .

노이즈 마진.

출력되는 신호 논리1이 뒷단 논리1의 범위안에 있어야 정상적으로 1이 전달된다.

따라서 555타이머를 TTL게이트에 연결할 수 있음.

주파수는 1mHz-100kHz까지 만들어낼 수 있음.

3가지 형태

-monostable

-bistable

-astable***>주로 씀: 주파수와 D조절하는 방법 배울 거임.

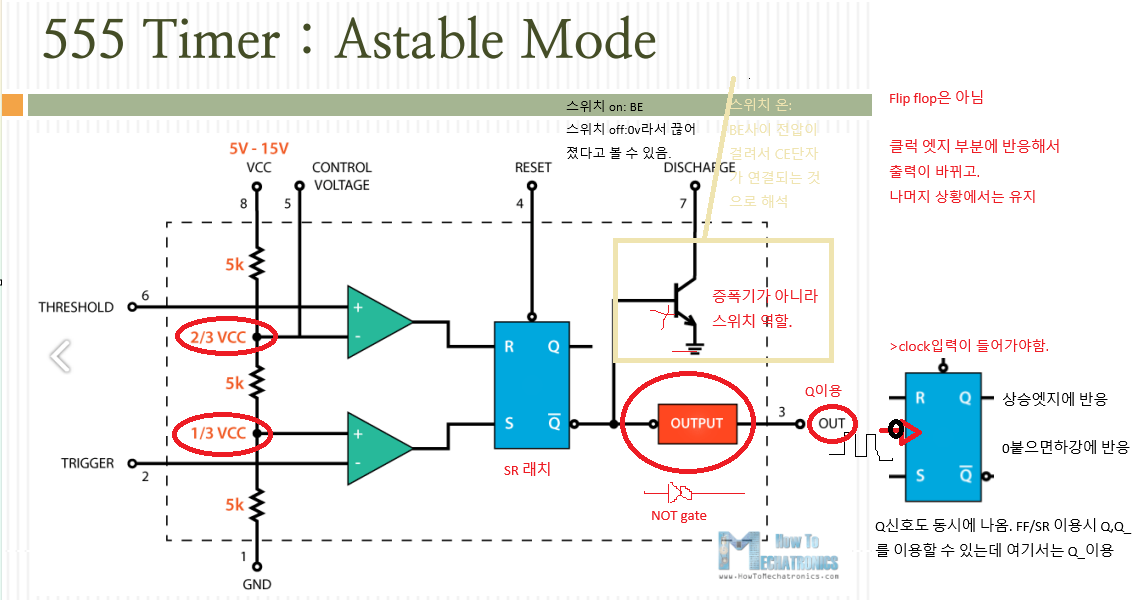

IC내부

2,6이 입력단자.

비교기로 들어감. (comparator)

나머지 전압은 VCC로 고정되어 저항으로 전압이 분배되어 있음.

위쪽 전압-단자는 2/3VCC가 들어감

아래전압 -단자은 1/3VCC가 들어감.

555타이머의 내부 동작

2번 ,6번 단자를 묶어서 동일한 입력을 넣음.

-Vin이 0-1/3VCC사이의 전압 입력을 넣음.

아래쪽 비교기에서는 +단자가 큼> 1출력

위쪽 비교기에서는 -단자의 전압이 큼. >0출력

SR래치에 1 0이 들어감.

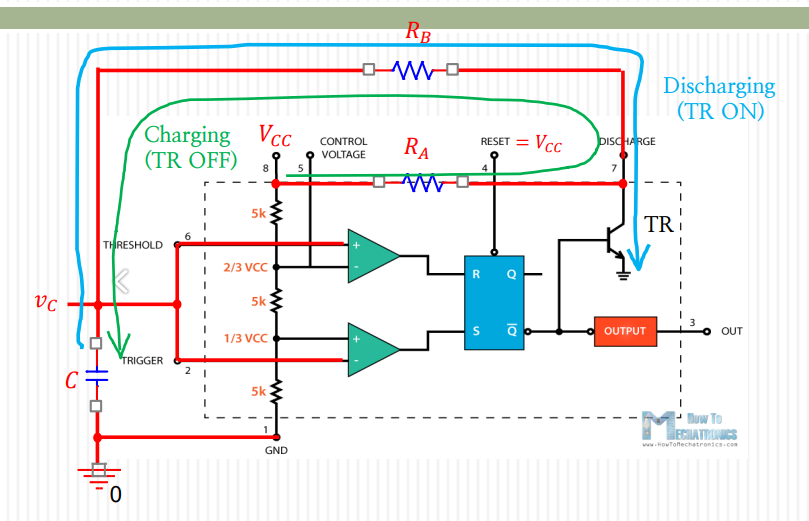

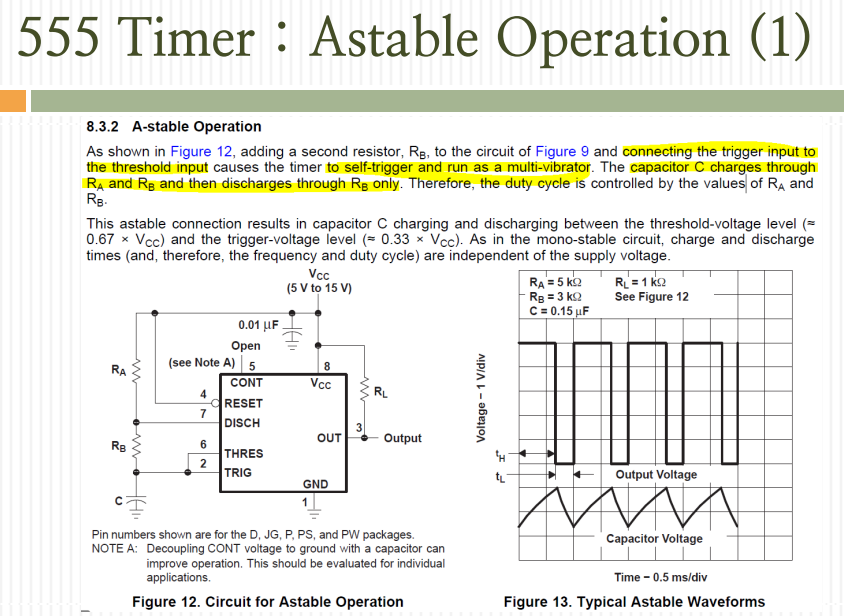

HOW to USE FOR ASTABLE

외부에서 입력을 넣는게 아니라

VIN에 커패시터와 저항을 달아줌. -Discharge에 연결

충방과정을달아주면 ASTABLE 회로 자동완성 성공!

정성적 해석.

C 전하 충전0

1/3VCC보다 작으므로 SR에 10이입력> 10> out 1이 나옴.

TR off > VCC에서 7과 연결되어서 RA,RB 경로를 따라서 C가 충전이 되어 Vc가 증가하다 HOLD상태가 된다.

유지하면서 Vc충전 >2/3VCC넘어가는 순간: SR에 01입력으로 바뀌어 출력 이 01>out 0으로 바뀜.

TRon> 7번 GND가 된다. (가장 낮은 전압) C로부터 전류가 GND로 흘러 방전이 회로가 된다. >HOLD 유지하면서 방전>

1/3VCC보다 낮아지면 앞의 과정을 반복.>펄스파 완성

링 회로랑 차이점: 앞의 회로는 방전, 충전회로가 같아서 시정수가 동일

여기서는 충방회로가 달라서 시정수가 다름.

충전:R=Ra+Rb *C

방전 R=Rb *C

101 한 바퀴가 한 주기

D를 바꾸는 방법.VCC를 주는 양, VCC전압 분배 값에 따라 D가 달라질 것이라 생각이 된다.XXXXX 아니었음

> RA,RB에 따라 시정수가 달라짐. 시정수가 크면 시간이 많이 걸림

RA가 클수록 시정수가 커짐 충전하는데 오래 걸림. 논리1로 나오는 펄스의 폭이 길어짐. (D를 바꿀 수 있음)

RA,RB를 통해 주파수를 결정.

RA를 0으로 쓰면. TR이 on이 순가 VCC-0V이 direct 연결되어 탐. 사실 안되는데.

가정 RA0이 되면 D가 50이 된다.

RA가 존재함으로 D가 >50%가된다.

RA가 얼마인가에 따라 D가 50보다 얼만큼 크게 만들것인가임.

스위칭 회로의 특성 (R연결)

TR B와 Q_의 연결에 저항을 연결해야함.

if 저항 연결을 안하면.

BJT이니까 B로 전류가 많이 흘러가게 된다.

nor 게이트의 전류가 10mA-20mA정도 내어줄 수 있는데, B으로 전류가 20ma로 많이 흐르게 되면 낫게이트로 전류가 흘러가지 않아 낫게이트가 동작을 하지 못함.

그래서 전류의 크기를 줄이기 위해 저항을 사용함

(저항의 역할: 전류의 크기를 줄인다. )

나머지 전류가 낫게이트로 들어감.

0 V에서 시작.

충전. 논리1 :충전

논리0: 방전.

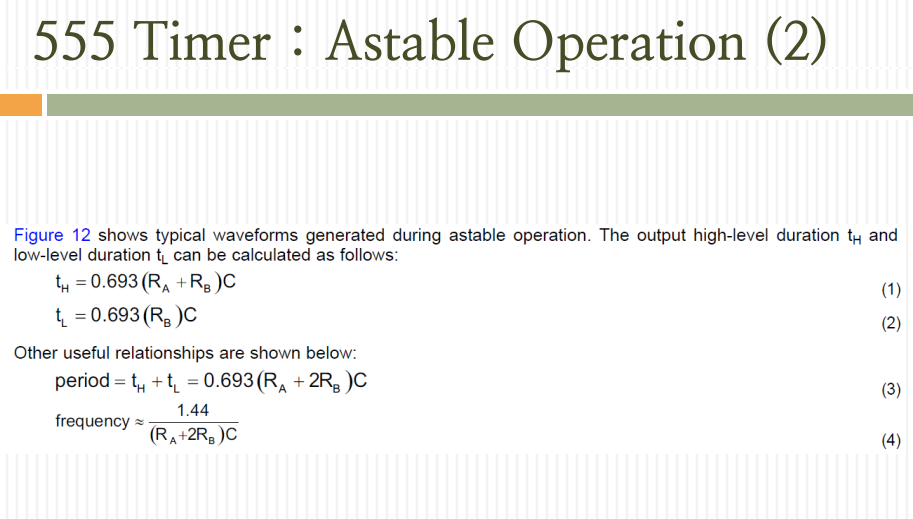

D는 충방전 시간이 결정함.

주파수를 알고 싶으면 충방시간의 합으로 구함.

충방전 시간이 데이터 시터로 제공이 된다.

충방전 시간의 합이 주기가 된다.

주파수는 주기의 역수

왼쪽 그래프 해석

-TL

방전 시간 찾기

V0=2/3VCC V무한대=0v 타우=RB*c

최종 전압은 1/3Vcc

충전시작.

Vo=1/3VCC V무한대=VCC 타우=(RA+RB)*C

RA,RB,C를 조절하면 주파수를 조절할 수 있다.

RA,RB에 따라 D조절 가능

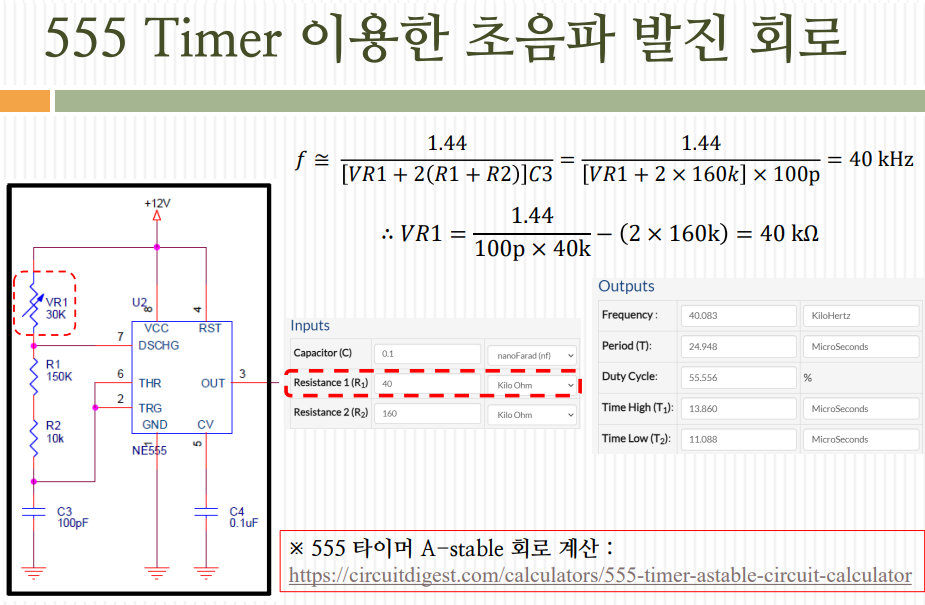

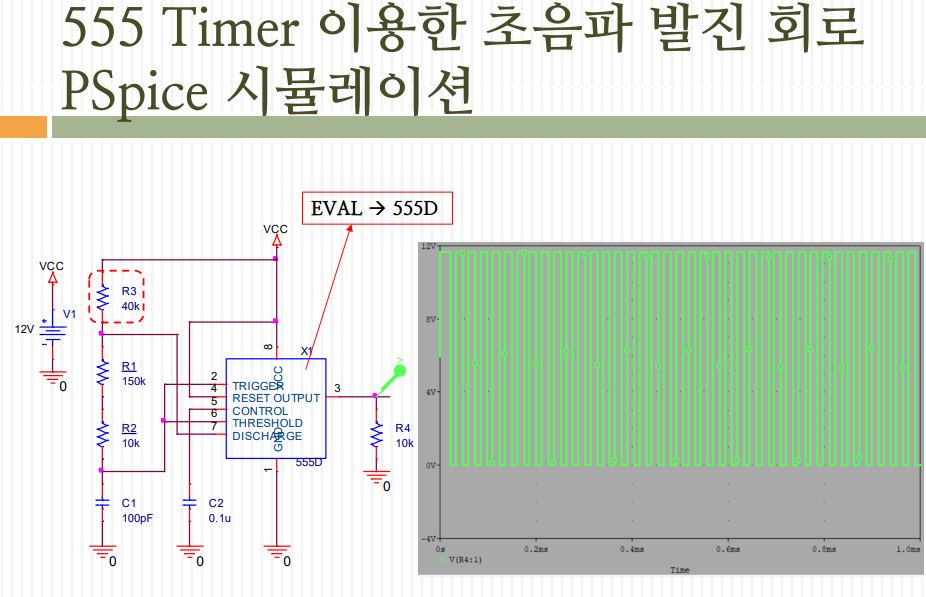

초음파를 펄스로 만들어내는 회로

C3 100pF

Rb 160k

f=40kHz

RA의 값을 구하기

>>40kohm

RA가 가변저항인 이유: 555타이머같은 회로를 이용하면 부품의 오차로 특정 갑에서 미묘하게 조정을 해야함.

가변 저항의 값으로 돌려서 맞추어야함.

출력파형의 가변적인 값을 맞추어서 해야함.

pulse fft를 하면

기본파 나오고 기본파의 정수배파가 하모닉으로 나오게 된다.

0v는 dc성분임.

수업 끝~~~~

'3-2학기 > 전자회로설계' 카테고리의 다른 글

| 20241126 Current Monitor(11장) Voltage Regulator and OP-AMP Applications(12장) (2) | 2024.11.26 |

|---|---|

| 전자회로설계 파일 (0) | 2024.10.05 |

| 9/24전자회로설계 (1) | 2024.10.05 |